“互聯網+稅務”環境下企業風險防范與納稅籌劃

隨著數字化時代的加速推進,互聯網與稅務管理的深度融合正在重塑企業的納稅環境和運營模式。在“互聯網+稅務”環境下,企業如何有效防范稅務風險,同時進行合理的納稅籌劃,已成為現代投資管理與咨詢中不可忽視的重要議題。

一、“互聯網+稅務”環境的特點與挑戰

“互聯網+稅務”并非簡單的技術疊加,而是通過大數據、云計算、人工智能等新技術手段,實現稅務管理的智能化、精準化和高效化。這一環境為企業帶來了諸多便捷,例如電子發票的普及、在線申報系統的完善,以及稅務數據的實時監控。它也帶來了新的挑戰:稅務監管更加透明嚴格,企業一旦出現數據不一致或操作失誤,可能面臨更高的稽查風險。

二、企業風險防范的關鍵措施

在“互聯網+稅務”背景下,企業需從以下幾個方面加強風險防范:

- 數據合規性管理:確保財務和稅務數據的真實性、完整性和一致性,避免因數據錯誤引發稅務問題。

- 系統安全與隱私保護:加強信息系統安全,防止數據泄露或被篡改,確保納稅信息的保密性。

- 持續監控與預警機制:利用數據分析工具,建立稅務風險預警系統,及時發現潛在問題并采取糾正措施。

- 員工培訓與意識提升:定期組織稅務法規培訓,增強員工對“互聯網+稅務”環境的認知,減少人為操作風險。

三、納稅籌劃的創新策略

納稅籌劃并非規避稅收,而是在合法合規的前提下,優化稅務結構,降低企業稅負。“互聯網+稅務”環境為企業提供了新的籌劃機會:

- 利用數據分析進行精準籌劃:通過分析企業運營數據,識別稅收優惠政策適用場景,例如研發費用加計扣除、區域稅收優惠等。

- 優化業務流程與結構:結合互聯網技術,調整供應鏈和業務模式,實現稅負的合理分攤。例如,通過設立分支機構或采用共享服務中心模式,優化增值稅和所得稅管理。

- 關注政策動態與科技工具:及時跟進國家稅收政策的變化,并應用智能稅務軟件輔助籌劃決策,提高籌劃效率和準確性。

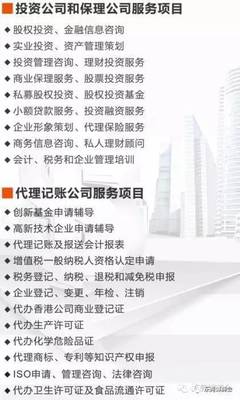

- 跨界合作與咨詢支持:在投資管理過程中,與專業稅務咨詢機構合作,借助外部專家資源,制定個性化的納稅籌劃方案。

四、投資管理與咨詢的整合應用

在“互聯網+稅務”時代,投資管理與咨詢應更加注重稅務因素的整合。企業可以通過以下方式實現協同:

- 在投資決策前期,進行稅務盡職調查,評估潛在稅務風險。

- 結合大數據分析,優化投資結構和退出策略,確保稅務成本最小化。

- 建立動態的稅務管理框架,將納稅籌劃融入企業戰略規劃中,提升整體投資回報率。

“互聯網+稅務”環境既是挑戰也是機遇。企業需積極適應這一變革,通過加強風險防范和優化納稅籌劃,在合規中謀求發展。投資管理與咨詢作為重要支撐,應幫助企業把握趨勢,實現可持續增長。隨著技術的不斷演進,企業還需持續學習與創新,以應對更加復雜的稅務環境。

如若轉載,請注明出處:http://www.belltoy.cn/product/39.html

更新時間:2026-04-08 10:12:22