CMOS集成電路設計(二) 接口電路詳解

在CMOS集成電路設計中,接口電路是連接芯片內(nèi)部邏輯與外部世界的關鍵橋梁。它不僅負責電平轉換和信號驅動,還承擔著保護內(nèi)部電路、確保信號完整性和實現(xiàn)不同系統(tǒng)間兼容的重要職責。本文將深入探討CMOS集成電路設計中幾種核心接口電路的工作原理、設計要點及應用場景。

一、輸入接口電路

輸入接口電路的主要功能是將外部信號(可能具有不同的電壓擺幅、噪聲容限和驅動能力)安全、可靠地轉換為芯片內(nèi)部CMOS邏輯能夠識別的信號。

- 施密特觸發(fā)器輸入:這是最常用的輸入緩沖電路之一。其核心特點是具有遲滯特性,即上升閾值電壓(VT+)高于下降閾值電壓(VT-)。這一特性使其對緩慢變化的信號或帶有嚴重噪聲的信號具有極強的抗干擾能力,能有效防止信號在閾值附近抖動造成的誤觸發(fā),從而產(chǎn)生干凈、陡峭的輸出波形。設計時需根據(jù)系統(tǒng)噪聲容限和信號速率合理設定遲滯窗口。

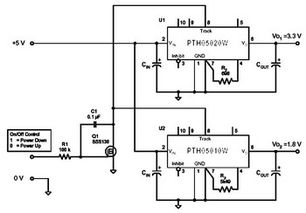

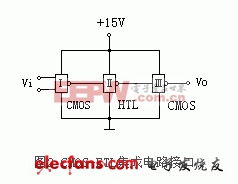

- 電平轉換輸入:當芯片需要與不同供電電壓的邏輯系統(tǒng)(如1.8V、3.3V、5V系統(tǒng))通信時,必須使用電平轉換電路。簡單的電阻分壓網(wǎng)絡可用于高壓到低壓的轉換,但會引入信號完整性和驅動能力問題。更可靠的方法是采用專用的電平轉換器電路,通常利用交叉耦合的PMOS/NMOS對,實現(xiàn)雙向或單向的、低延遲的電平適配。

- ESD保護電路:所有輸入/輸出引腳都必須集成靜電放電保護電路。典型的ESD保護結構包括基于二極管、柵接地NMOS或可控硅整流器的初級和次級保護網(wǎng)絡,旨在將人體模型或機器模型產(chǎn)生的瞬間高壓大電流安全泄放到電源或地線,防止脆弱的柵氧化層被擊穿。

二、輸出接口電路

輸出接口電路的核心任務是將內(nèi)部微弱的邏輯信號放大,以足夠的電流和電壓驅動外部負載(如PCB走線、其他芯片的輸入、LED等)。

- 推挽輸出級:這是最經(jīng)典和常見的輸出結構,由一個上拉PMOS管和一個下拉NMOS管組成互補對。其優(yōu)點是結構簡單、驅動能力強、輸出電阻低、高低電平擺幅接近電源軌。設計關鍵在于晶體管的尺寸(寬長比),需要根據(jù)所需的驅動電流、上升/下降時間以及功耗進行折衷優(yōu)化。過大的驅動能力會增加開關噪聲和功耗。

- 開漏輸出:這種結構只有下拉NMOS管,沒有內(nèi)部上拉。輸出高電平需要依賴外部上拉電阻連接到電源。開漏輸出的主要優(yōu)點是便于實現(xiàn)“線與”邏輯功能,以及方便進行不同電壓域的電平轉換(只需改變上拉電阻的電源電壓)。在I2C等總線協(xié)議中廣泛應用。但其缺點是上升時間由外部RC常數(shù)決定,速度較慢,且靜態(tài)功耗可能較高。

- 三態(tài)輸出:在總線應用中,多個驅動源需要共享同一物理線路。三態(tài)輸出在推挽結構的基礎上增加了一個使能控制端。當使能無效時,上下兩個驅動管均關閉,輸出呈現(xiàn)高阻態(tài),從而與總線隔離。這使得多個器件可以分時復用總線而互不干擾。

三、雙向輸入/輸出接口

許多芯片引腳(如存儲器數(shù)據(jù)線、微控制器GPIO)需要根據(jù)操作模式在輸入和輸出功能間切換,這就需要雙向I/O電路。其本質(zhì)是輸入緩沖器、輸出驅動器和三態(tài)控制邏輯的巧妙組合,并通過方向控制信號進行管理。設計時需特別注意避免當方向切換瞬間或配置錯誤時,輸出驅動與外部輸入信號發(fā)生沖突(“爭用”),導致大電流甚至損壞電路。

四、高速接口電路

隨著數(shù)據(jù)速率進入Gb/s范圍,接口設計面臨信號完整性(如反射、串擾、碼間干擾)的嚴峻挑戰(zhàn)。此時,簡單的CMOS推挽結構已力不從心。

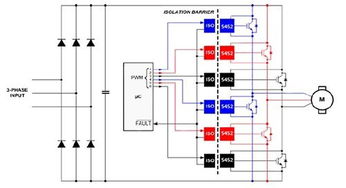

- 電流模邏輯與低壓差分信號:CML和LVDS采用差分信號傳輸,以恒定或受控的電流源驅動終端電阻。差分架構對共模噪聲有極強的抑制能力,電壓擺幅小(通常幾百毫伏),開關速度快,功耗相對可控,是芯片間高速串行通信(如SerDes)的主流技術。

- 片上終端匹配:為了抑制高速信號在傳輸線末端的反射,需要在驅動器或接收器端集成匹配電阻(如50歐姆)。片上終端節(jié)省了PCB空間和元件,但需要精確的電阻工藝和校準電路來應對工藝、電壓、溫度的變化。

- 預加重與均衡:為了補償信道的高頻損耗,在發(fā)送端采用預加重技術,預先增強信號的高頻分量;在接收端則采用均衡器(如連續(xù)時間線性均衡器CTLE或判決反饋均衡器DFE),來補償衰減,睜開數(shù)據(jù)眼圖。

接口電路的設計是CMOS集成電路設計中兼具藝術性與工程性的環(huán)節(jié)。設計師必須在驅動能力、速度、功耗、噪聲、面積、可靠性以及系統(tǒng)兼容性之間做出精妙的權衡。隨著工藝進步和系統(tǒng)需求日益復雜,接口電路,特別是高速SerDes和高速存儲接口(如DDR/LPDDR),已成為許多SoC芯片中技術最密集、設計挑戰(zhàn)最大的模塊之一。理解并掌握各類接口電路的原理與設計方法,是成為一名優(yōu)秀集成電路工程師的必經(jīng)之路。

如若轉載,請注明出處:http://www.belltoy.cn/product/55.html

更新時間:2026-01-05 13:02:32