超大規模集成電路設計 技術、流程與挑戰

超大規模集成電路(VLSI)設計是電子工程領域的核心技術之一,它涉及在微小的硅片上集成數百萬甚至數十億個晶體管,實現復雜的功能模塊,如處理器、存儲器和專用集成電路(ASIC)。隨著摩爾定律的推進,VLSI 設計在現代電子設備中扮演著至關重要的角色,從智能手機到數據中心,無處不在。

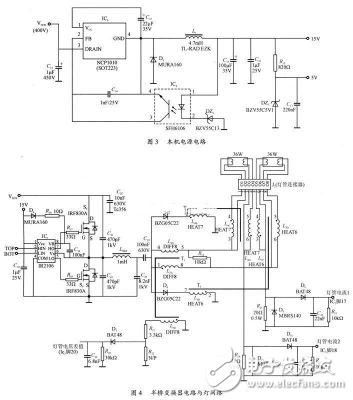

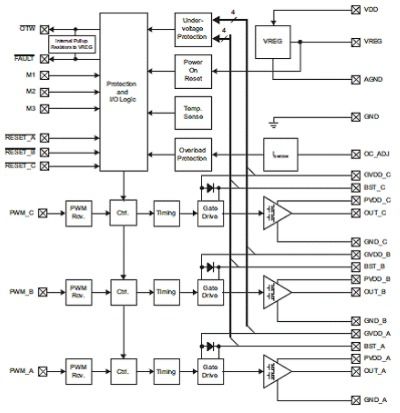

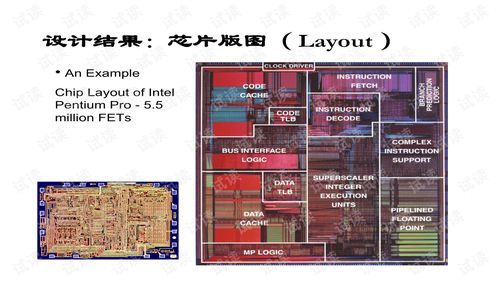

VLSI 設計流程通常包括多個階段:首先是系統規格定義,明確芯片的功能、性能和功耗要求;接著是架構設計,確定整體結構和模塊劃分;然后是邏輯設計,使用硬件描述語言(如 Verilog 或 VHDL)實現電路邏輯;之后是物理設計,涉及布局布線,確保電路在硅片上的正確實現;最后是驗證和測試,通過仿真和實際測試來保證芯片的可靠性和性能。整個過程需要依賴先進的電子設計自動化(EDA)工具來管理復雜性。

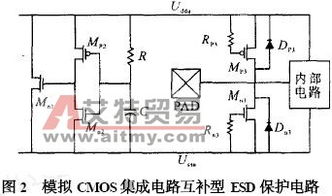

在 VLSI 設計中,關鍵技術包括 CMOS 工藝、低功耗設計、時序分析和可測試性設計。隨著工藝節點不斷縮小至納米級別,設計者面臨著諸多挑戰,如功耗管理、信號完整性、熱效應和制造成本上升。例如,在先進制程下,漏電流和互連延遲成為關鍵問題,需要采用多電壓域、時鐘門控等技術來優化。

未來,VLSI 設計正朝著 3D 集成、異構計算和人工智能加速器方向發展,以應對數據爆炸和能效需求。同時,開源 EDA 工具和設計方法的興起,正在降低設計門檻,推動創新。超大規模集成電路設計不僅是技術進步的引擎,也是推動數字化轉型的核心力量,其發展將持續塑造電子產業的未來。

如若轉載,請注明出處:http://www.belltoy.cn/product/5.html

更新時間:2026-01-07 19:39:54